香港中文大學

The Chinese University of Hong Kong

# CENG3430 Rapid Prototyping of Digital Systems Lecture 04: Combinational Circuit and Sequential Circuit

# Ming-Chang YANG

mcyang@cse.cuhk.edu.hk

11111111

# **Recall: Concurrent vs. Sequential**

#### Concurrent Statement

- ① Statements inside the architecture body can be executed concurrently, except statements enclosed by a process.

- ② Every statement will be <u>executed once</u> whenever <u>any</u> <u>signal in the statement</u> changes.

#### Sequential Statement

- ① Statements within a **process** are executed sequentially, and the result is obtained when the process is complete.

- ② process (sensitivity list): When one or more signals in the sensitivity list change state, the process executes once.

- ③ A process can be treated as one concurrent statement in the architecture body.

CENG3430 Lec03: Architectural Styles of VHDL

## **Recall: Concurrent vs. Sequential**

| <b>Concurrent Statement</b>       | Sequential Statement                             |

|-----------------------------------|--------------------------------------------------|

| when-else                         | if-then-else                                     |

| b <= "1000" when a = "00" else    | if a = "00" then b <= "1000"                     |

| "0100" when <b>a = "01</b> " else | elsif <b>a = "01"</b> then <b>b &lt;= "1000"</b> |

| "0010" when <b>a = "10</b> " else | elsif <b>a = "10"</b> then <b>b &lt;= "1000"</b> |

| "0001" when <b>a = "11";</b>      | else b <= "1000"                                 |

|                                   | end if;                                          |

| with-select-when                  | case-when                                        |

| with a select                     | case a is                                        |

| b <= "1000" when "00",            | when "00" => b <= "1000";                        |

| "0100" when "01",                 | when "01" => b <= "0100";                        |

| "0010" when "10",                 | when <b>"10"</b> => <b>b &lt;= "0010";</b>       |

|                                   |                                                  |

| "0001" when "11";                 | when <b>others</b> => <b>b</b> <= "0001";        |

#### Outline

- Combinational Circuit and Sequential Circuit

- Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

# **Combinational Circuit**

- Combinational Circuit: no memory

- Outputs are a function of the *present* inputs only.

- As soon as inputs change, the values of previous outputs are lost.

- It has no internal state (i.e., has no memory).

- Common Examples: Full/Half Adders (*Lab01*), Encoders/Decoders (*Lab02*), Multiplexers (*Lab03*), Bi-directional Bus (*Lec04*), etc.

- Rule: You can build a combinational circuit using <u>either</u> concurrent or sequential (i.e., process) statements.

# **Combinational Logic as a Process**

• Consider a simple combinational logic:

c <= a and b;

• This logic can be also modeled as a process:

- All signals referenced in process must be in sensitivity list. entity And Good is

port (a, b: in std\_logic; c: out std\_logic); end And\_Good; architecture Synthesis Good of And Good is

begin

process (a, b) -- sensitive to signals a and/or b

begin

c <= a and b; -- c updated

#### end process;

end;

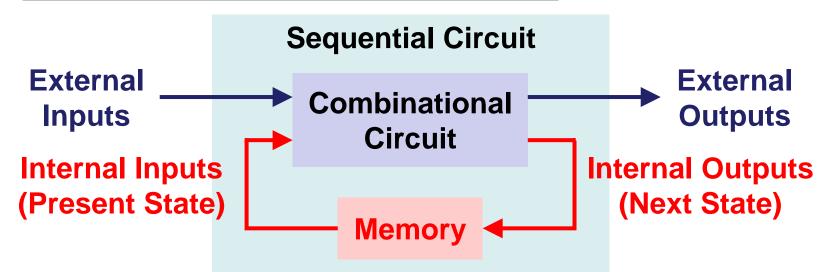

# **Sequential Circuit**

#### Sequential Circuit: has memory

- Outputs are a function of <u>the present inputs</u> and <u>the</u> <u>previous</u> outputs (i.e., the **internal state**).

- It changes outputs based on <u>inputs</u>; but the outputs also depend upon <u>previous outputs</u> (i.e., the **internal state**) (i.e., has <u>memory</u>).

- Example: Latch (*Lec04*), Flip-Flops (*Lec04*), Counters (*Lec05*), etc.

- Rule: You must build a sequential circuit with <u>only</u> sequential (i.e., process) statements.

# **Combinational vs. Sequential Circuit**

#### Combinational Circuit: no memory

- ① Outputs are a function of the *present* inputs only.

- ② Rule: Use either concurrent or sequential statements.

- Sequential Circuit: has memory

- ① Outputs are a function of <u>the present inputs</u> and <u>the previous outputs</u> (i.e., the **internal state**).

- ② Rule: Must use <u>sequential (i.e., process</u>) statements.

## Outline

#### Combinational Circuit and Sequential Circuit

- Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

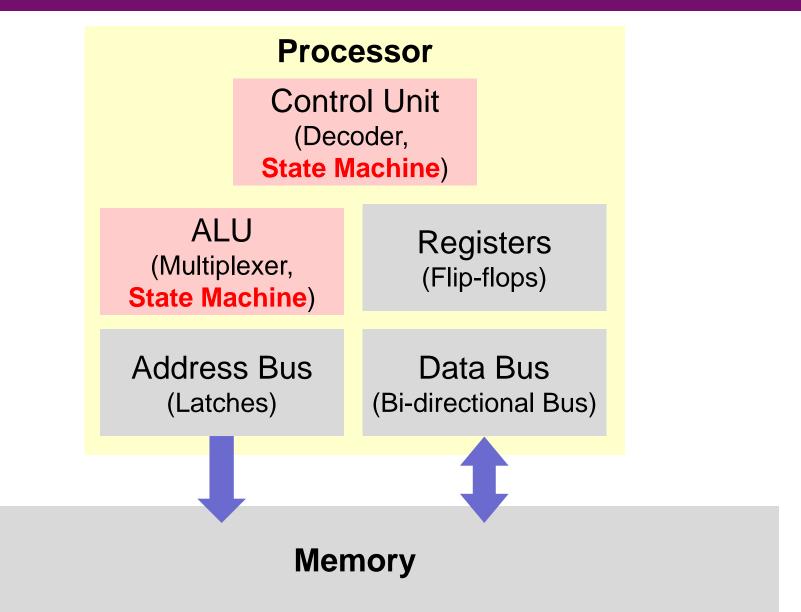

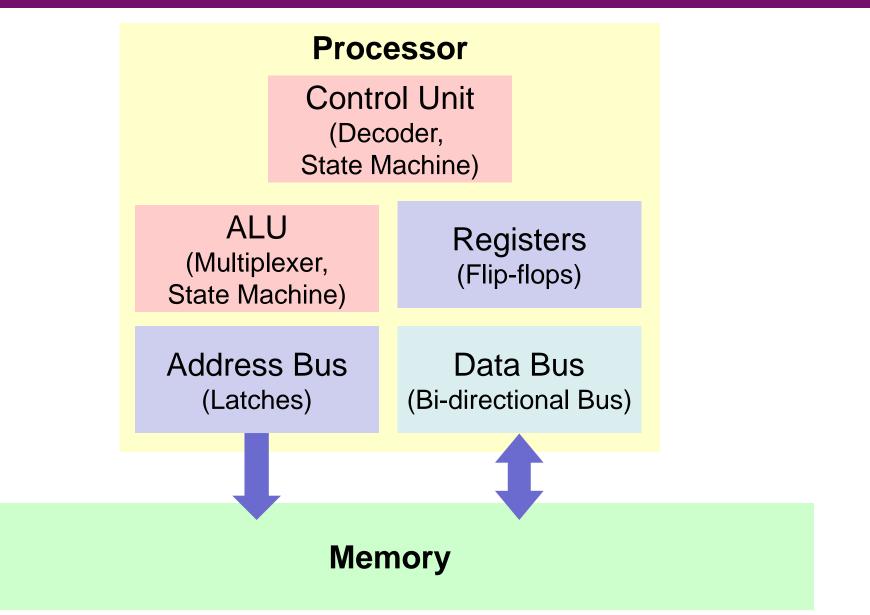

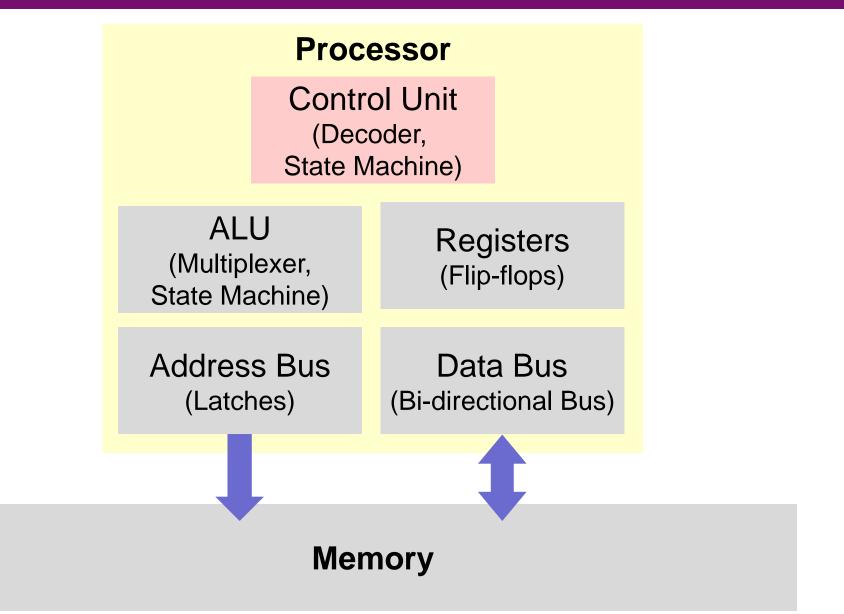

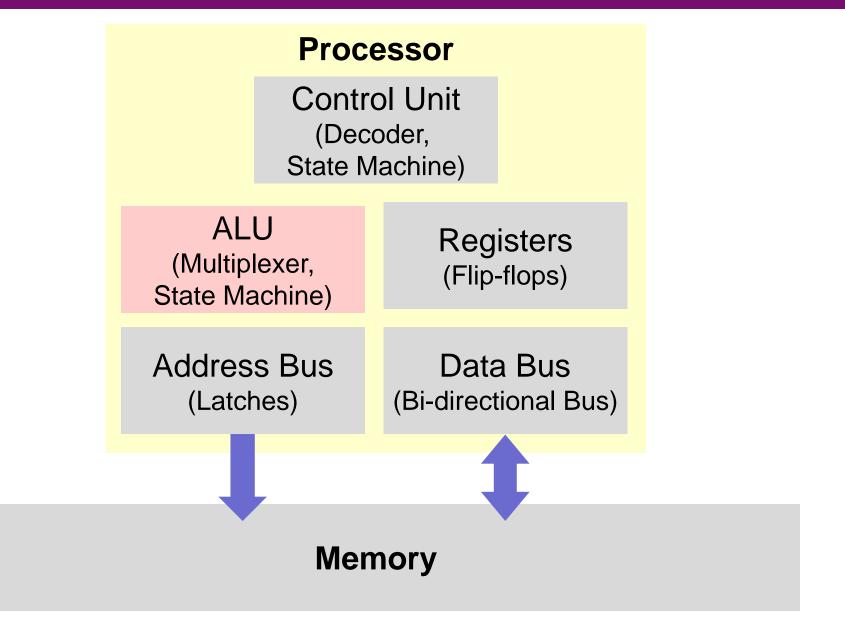

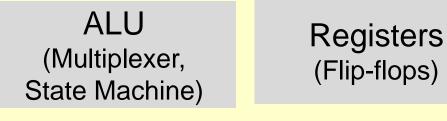

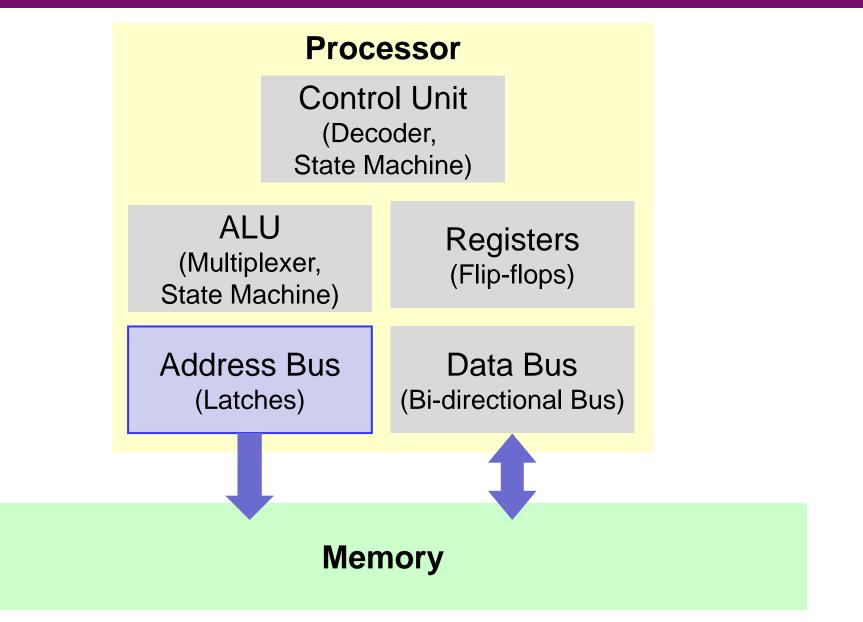

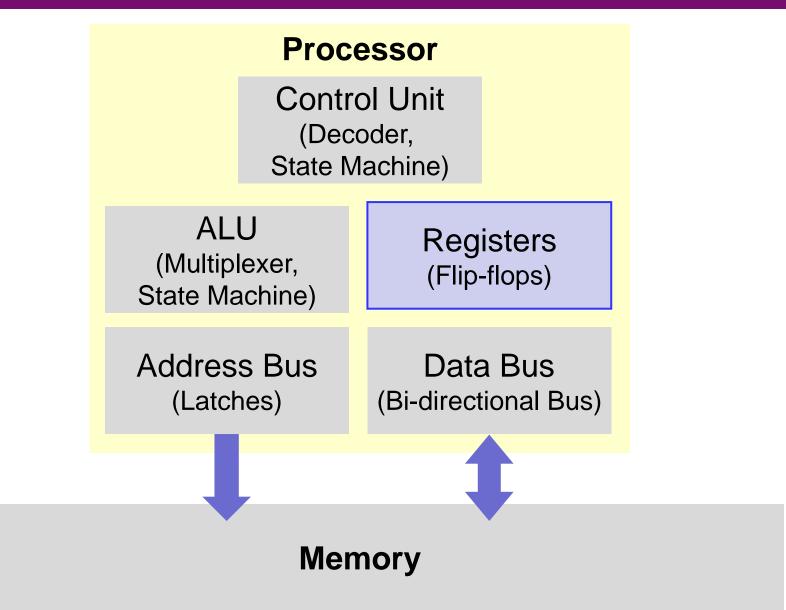

## **Typical Processor Organization**

## Outline

#### Combinational Circuit and Sequential Circuit

- Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

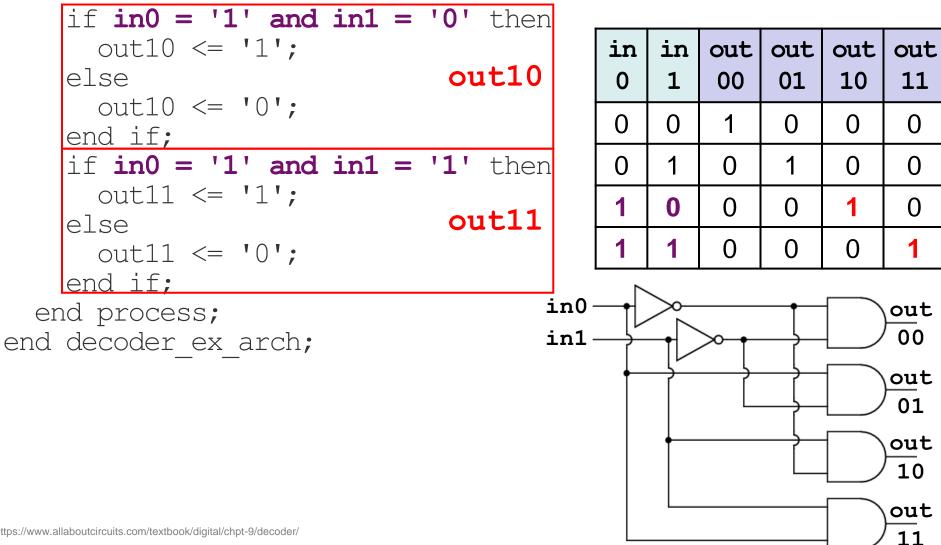

#### **Building Blocks: Decoder**

# **Combinational Circuit: Decoder (1/2)**

```

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity decoder_ex is

port (in0,in1: in std_logic;

out00,out01,out10,out11: out std_logic);

end decoder_ex;

architecture decoder_ex_arch of decoder_ex is

begin

```

```

process (in0, in1)

```

begin

| if in0 = '0' and in1 = | <b>= '0'</b> then |

|------------------------|-------------------|

| out00 <= '1';          |                   |

| else                   | out00             |

| out00 <= '0';          |                   |

| end if;                |                   |

| if in0 = '0' and in1 = | <b>= '1'</b> then |

| out01 <= '1';          |                   |

| else                   | out01             |

| out01 <= '0';          |                   |

| end if;                |                   |

| in<br>O | in<br>1 | out<br>00 | out<br>01 | out<br>10 | out<br>11 |

|---------|---------|-----------|-----------|-----------|-----------|

| 0       | 0       | 1         | 0         | 0         | 0         |

| 0       | 1       | 0         | 1         | 0         | 0         |

| 1       | 0       | 0         | 0         | 1         | 0         |

| 1       | 1       | 0         | 0         | 0         | 1         |

## **Combinational Circuit: Decoder (2/2)**

14

https://www.allaboutcircuits.com/textbook/digital/chpt-9/decoder/

## **Class Exercise 4.1**

| Student ID: |  |

|-------------|--|

| Name:       |  |

Date:

);

• Implement the Encoder based on the given table: port(

architecture encoder\_ex\_arch of encoder\_ex is begin process ( ) begin

| end process;                                                                         |

|--------------------------------------------------------------------------------------|

| end encoder ex arch;<br>CENG3430 Lec04: Combinational Circuit and Sequential Circuit |

| in | in | in | in | out | out |

|----|----|----|----|-----|-----|

| 00 | 01 | 10 | 11 | 0   | 1   |

| 1  | 0  | 0  | 0  | 0   | 0   |

| 0  | 1  | 0  | 0  | 0   | 1   |

| 0  | 0  | 1  | 0  | 1   | 0   |

| 0  | 0  | 0  | 1  | 1   | 1   |

## Outline

#### Combinational Circuit and Sequential Circuit

- Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

## **Building Blocks: Multiplexer**

# **Combinational Circuit: Multiplexer**

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity mux ex is

port (in1, in2, sel: in std logic;

out1: out std logic);

end mux ex;

architecture mux ex arch of mux ex is

begin

process (in1, in2, sel)

begin

if sel = '0' then

out1 <= in1; -- select in1

else

out1 <= in2; -- select in2</pre>

end if;

end process;

end mux ex arch;

```

CENG3430 Lec04: Combinational Circuit and Sequential Circuit

7

MUX

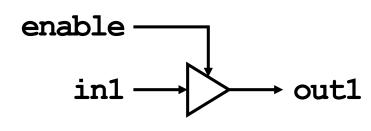

#### **Recall: Tri-state Buffer**

| in1 | enable | out1 |

|-----|--------|------|

| 0   | 0      | Z    |

| 1   | 0      | Z    |

| 0   | 1      | 0    |

| 1   | 1      | 1    |

# outl <= inl when enable = '1' else 'Z'; end tri\_ex\_arch; CENG3430 Lec04: Combinational Circuit and Sequential Circuit</pre>

## **Class Exercise 4.2**

| Student ID: | <br>Date: |

|-------------|-----------|

| Name:       |           |

Specify the I/O signals in the circuit:

```

entity mux ex is

port (in1, in2, sel: in std logic;

out1: out std logic);

end mux ex;

architecture mux ex arch of mux ex is

begin

process (in1, in2, sel)

begin

if sel = '0' then

out1 <= in1;</pre>

else

out1 \leq in2;

MUX

end if;

end process;

end mux ex arch;

```

## Outline

#### Combinational Circuit and Sequential Circuit

- Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

## **Building Blocks: Bi-directional Bus**

Control Unit (Decoder, State Machine)

Memory

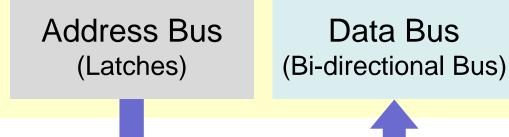

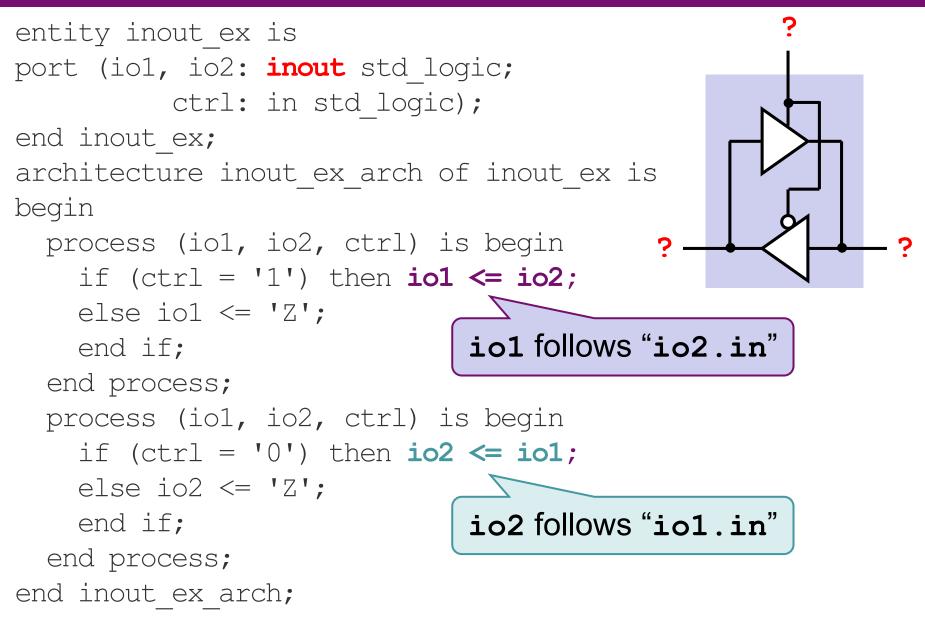

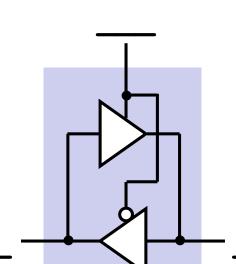

## **Combinational Circuit: Bi-directional Bus**

## **Class Exercise 4.3**

entity inout ex is port (io1, io2: inout std logic; ctrl: in std logic); end inout ex; architecture inout ex arch of inout ex is begin process (iol, io2, ctrl) is begin if (ctrl = '1') then **iol <= io2**; else iol  $\leq 'Z'$ ; end if; end process; process (iol, io2, ctrl) is begin if (ctrl = '0') then io2 <= io1; else io $2 \leq 'Z';$ end if; end process; end inout ex arch;

CENG3430 Lec04: Combinational Circuit and Sequential Circuit

• Specify I/O signals:

Date:

Student ID: \_\_\_\_

Name:

## Outline

#### Combinational Circuit and Sequential Circuit

#### Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

# **Latches and Flip Flops**

- Latches and Flip-flops (FF) are the basic elements used to store information.

- Each latch and flip flop can keep one bit of data.

- The main difference between latch and flip-flop:

- A latch continuously checks input and changes the output whenever there is a change in input.

- A latch has **no** clock signal.

- A flip-flop continuously checks input and changes the output only at times determined by the clock signal.

- A flip flop has a clock signal.

## Outline

#### Combinational Circuit and Sequential Circuit

#### Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

#### **Building Blocks: Latch**

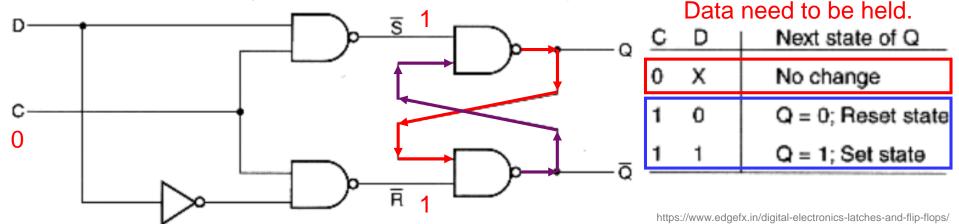

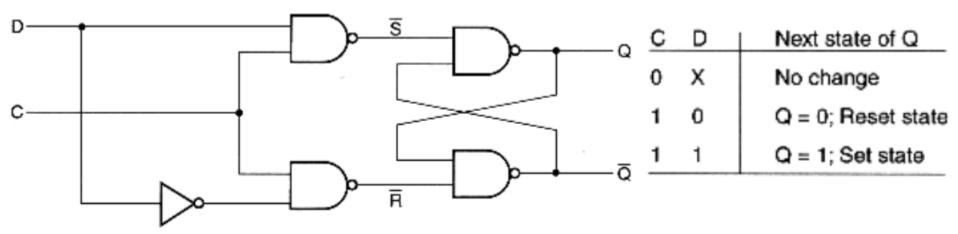

# Sequential Circuit: Latch (1/2)

- Latches are asynchronous (no CLOCK signal).

- It changes output only in response to input.

- Case Study: D Latch

- When enable line C is high, the output Q follows input D.

- $\rightarrow$  That is why D latch is also called as transparent latch.

- When enable line C is asserted, the latch is said to be transparent.

- When C falls, the last state of D input is trapped and held.

- $\rightarrow$  That is why the latch has memory!

# Sequential Circuit: Latch (2/2)

| 2  | use  | ary IEEE;(ok vivad<br>IEEE.STD_LOGIC_1164<br>ty latch_ex is |        | 4. | 4)   | $\rightarrow$ D Q $\rightarrow$                               |

|----|------|-------------------------------------------------------------|--------|----|------|---------------------------------------------------------------|

| 4  | port | : (C, D: in std_logic                                       | C;     |    |      | $\rightarrow$ C                                               |

| 5  |      | Q: out std_log                                              | LC);   |    |      |                                                               |

| 6  | end  | latch_ex;                                                   |        |    |      |                                                               |

| 7  | arch | nitecture latch ex an                                       | rch of | 1  | atch | ex is                                                         |

| 8  | begi |                                                             |        |    | -    | _                                                             |

| 9  | pı   | rocess(C, D) sensi                                          | itivit | У  | list |                                                               |

| 10 | be   | egin                                                        |        | -  | _    |                                                               |

| 11 |      | if $(C = '1')$ then                                         | -      | C  | D    | Next state of Q                                               |

| 12 |      | Q <= D;                                                     |        | 0  | Х    | No change                                                     |

| 13 |      | end if;                                                     | —×ē    | 1  | 0    | Q = 0; Reset state                                            |

|    |      | no change (memory                                           | 7)     |    |      |                                                               |

| 14 | er   | nd process;                                                 | Ľ      | 1  | 1    | Q = 1; Set state                                              |

| 15 | end  | latch_ex_arch;                                              |        |    | http | s://www.edgefx.in/digital-electronics-latches-and-flip-flops/ |

#### **Class Exercise 4.4**

| Studen <sup>-</sup> | t ID: |  |

|---------------------|-------|--|

| Name:               |       |  |

Date:

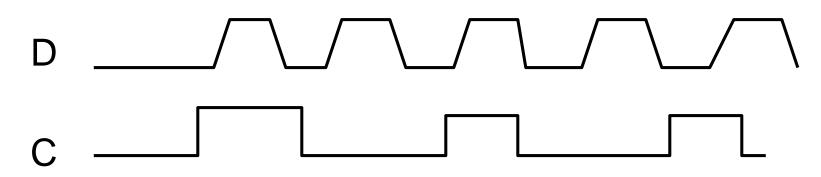

• Given a D latch, draw Q in the following figure:

Q

## Outline

#### Combinational Circuit and Sequential Circuit

#### Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

## **Building Blocks: Flip-flops**

# Sequential Circuit: Flip-flop

- A Latch is a non-clock-controlled memory device.

- ① It has **no** CLOCK signal.

- ② It changes output only in response to <u>data input</u>. (i.e., the value is set asynchronously).

- A Flip-flop (FF) is a clock-controlled memory device.

- ① Different from a Latch, it has a <u>CLOCK signal</u> as input.

- ② It stores the input value (i.e., low or high) and outputs the stored value only in response to the <u>CLOCK signal</u>.

- Positive-Edge-Triggered: At every low to high of CLOCK.

- Negative-Edge-Triggered: At every high to low of CLOCK.

- ③ The value can be **reset** asynchronously or synchronously.

- Async. Reset: Reset the value anytime.

- Sync. Reset: Reset the value on positive or negative clock edges.

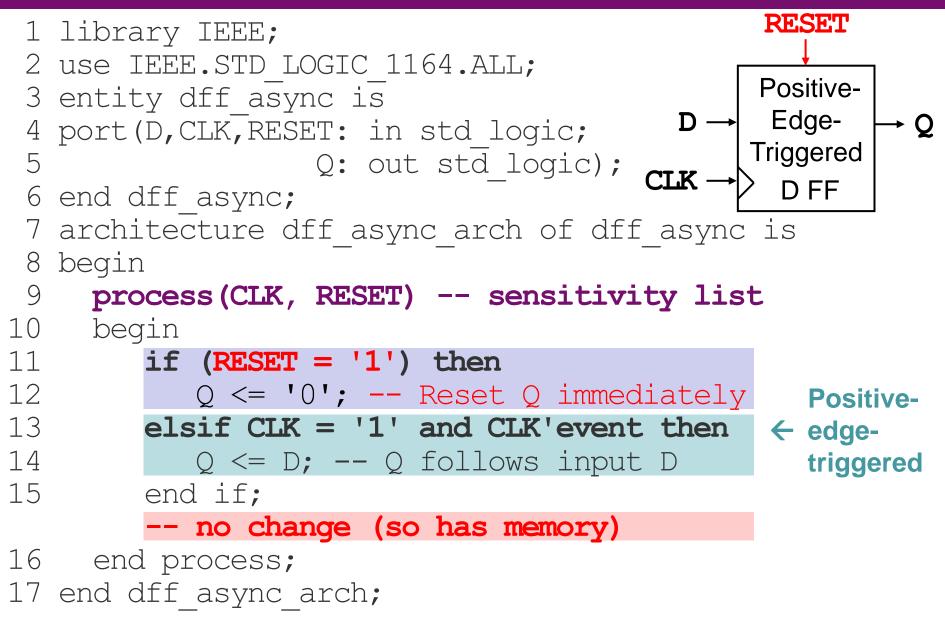

# Positive-Edge-Triggered FF with Async. Reset

# **Recall: Attributes (Lec01)**

- Another important signal attribute is the 'event.

- This attribute yields a Boolean value of TRUE if an event has just occurred on the signal.

- It is used primarily to determine if a clock has transitioned.

- Example (*more in Lec04*):

•••

...

# if clock = '1' and clock'event then my\_out <= my\_in;</pre>

# **Class Exercise 4.5**

| Student | ID: |

|---------|-----|

| Name:   |     |

Date:

• Consider the following VHDL implementation of a positive-edge-triggered FF with asynchronous reset:

```

9

process(CLK, RESET) -- sensitivity list

begin

10

if (RESET = '1') then

11

Q <= '0'; -- Reset Q

12

13

elsif CLK = '1' and CLK' event then

14

Q \leq D; --Q follows input D

end if;

15

-- no change (so has memory)

16

end process;

– When will line 9 be executed?

Answer:

```

– Which signal is more "powerful"? CLK or RESET? Answer:

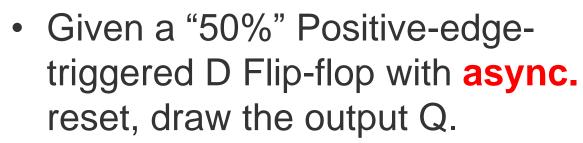

## **Class Exercise 4.6**

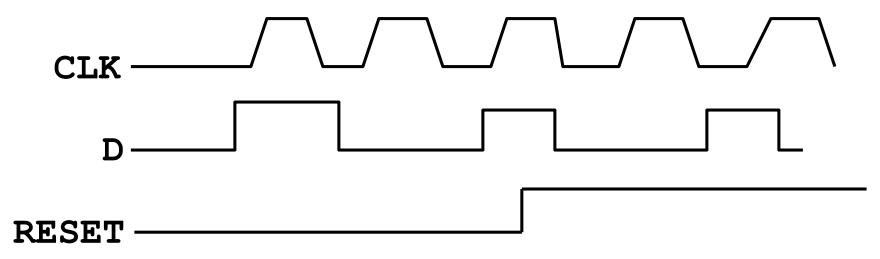

- "50%" means it changes state when clock is 50% between high and low.

Date:

43

Student ID: \_\_\_\_

Name:

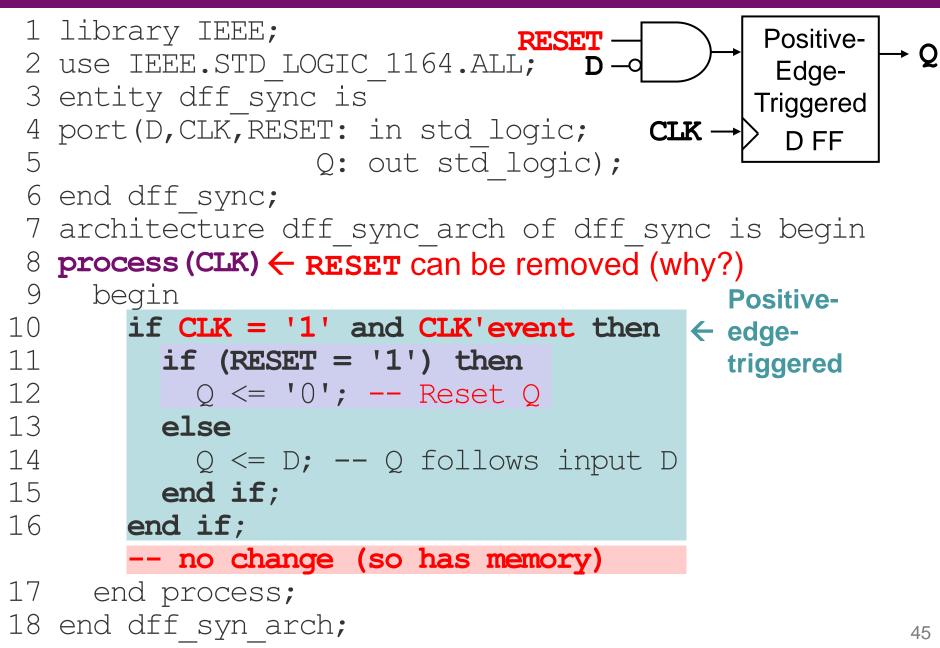

# Positive-Edge-Triggered FF with Sync. Reset

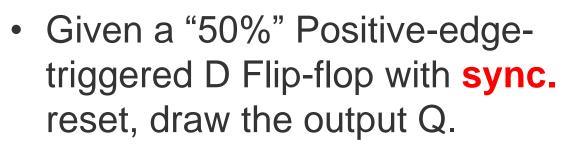

# **Class Exercise 4.7**

- "50%" means it changes state when clock is 50% between high and low.

Student ID: \_\_\_\_

Name:

Date:

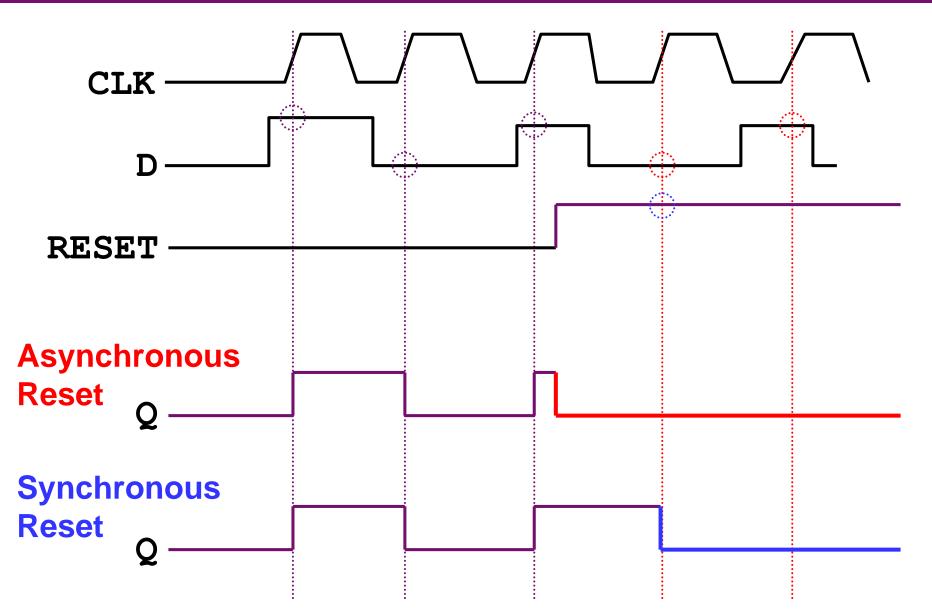

# Async. Reset vs. Sync. Reset (1/2)

• The order of the statements inside the process determines asynchronous reset or synchronous reset.

– Asynchronous Reset (check RESET first!)

11 if (RESET = '1') then 12 Q <= '0'; -- Reset Q 13 elsif CLK = '1' and CLK'event then 14 Q <= D; -- Q follows input D 15 end if;

– Synchronous Reset (check CLK first!)

| 10 | if $CLK = '1'$ and $CLK'$ event then |

|----|--------------------------------------|

| 11 | if (RESET = $'1'$ ) then             |

| 12 | Q <= '0'; Reset Q                    |

| 13 | else                                 |

| 14 | Q <= D; Q follows input D            |

| 15 | end if;                              |

| 16 | end if;                              |

## Aysnc. Reset vs. Sync. Reset (2/2)

# Summary

- Combinational Circuit and Sequential Circuit

- Building Blocks of a Processor

- Combinational Circuit: No Memory

- Decoder

- Multiplexer

- Bi-directional Bus

- Sequential Circuit: Has Memory

- Latch

- Flip-flop with Asynchronous Reset

- Flip-flop with Synchronous Reset

## What's the next? Finite State Machine